(3 Hours) Max. marks: 80

- **N.B.:** (1) Question No. 1 is compulsory.

- (2) Solve any three questions from the remaining five questions.

- (3) Figures to the right indicate full marks.

- (4) Assume suitable data if necessary and mention the same in answer sheet.

## Q.1 Attempt any 5 questions.

120

- a) Explain bleeder resistor and critical inductance

- b) Draw and explain small signal model of FET

- c) Explain VI characteristics of PN junction diode

- d) State and explain Millers Theorem

- e) Why should RC be as large as possible in the design of CE amplifier?

- f) Design a self bias circuit using JFET for  $I_D$ =3mA,  $V_{DD}$ =20V,  $V_{DS}$ =0.6 $V_{DD}$  ( $I_{DSS}$ =8mA,  $V_{DD}$ = 4V)

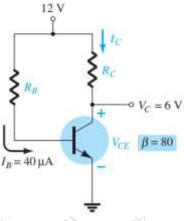

- Q.2 a) Given the information in the circuit diagram Fig. 2(b) determine

(a) Ic (b)  $R_C$  and (c)  $R_B$

Fig. 2 (b)

- b) Define stability factor (S) and explain factors affecting S.Derive the expression for stability factor of collector to base bias circuit

- c) For JFET is IDSS = 6mA, Vp=-6V,  $rd=\Box$ , Cgd=4pF, Cgs=6pF, [05] Cds=1pF. Determine VGSQ, IDQ, gmo, gm and midband voltage gain Av

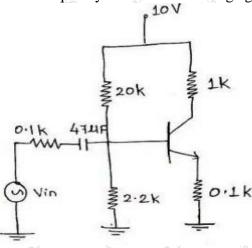

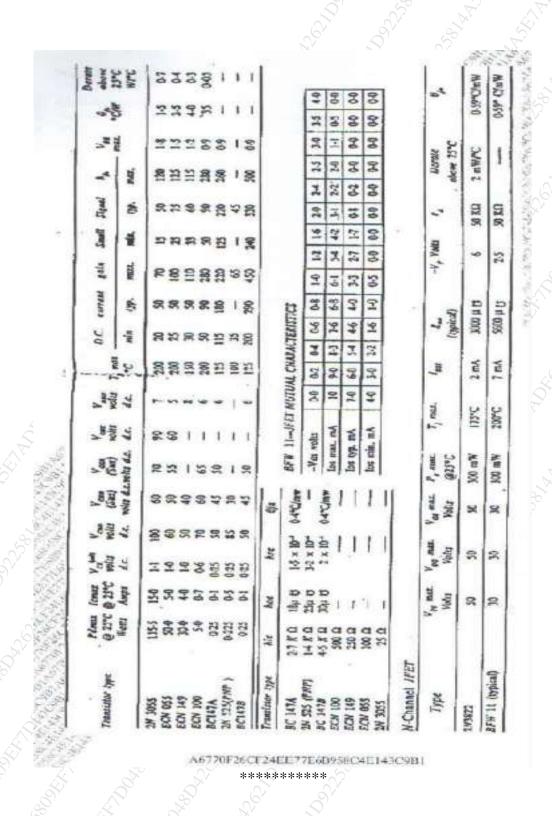

- **Q.3** a) Design the resistors of a single stage CS amplifier for audio frequency with BFW11 with  $I_{DS} = (3.3 \pm 0.6)$  mA and  $A_V = 12$ .

- b) Draw CS JFET amplifier with self bias circuit and derive the expression [10] for voltage gain, input impedance and output impedance

- Q.4 a) Explain concept of shunt zener regulator. For the shunt zener regulator giving output voltage of 10 V and load resistance varying from  $5K\Omega$  to  $10K\Omega$ , Vin is varying between 18V to 22V. Find Rs, Pzmax, Sv and Ro. Assume Rz =  $4\Omega$  and Izmin =  $50\mu$ A

12840 Page 1 of 4

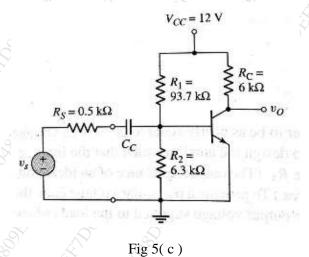

- b) For the circuit shown below in Fig. 4(b), the transistor parameters are VBE(on) = 0.7V,  $\beta$ =200, VA=  $\Box$

- i) Derive the expression for lower cutoff frequency (or time constant) due to input coupling capacitor

- ii) Determine lower cutoff frequency and midband voltage gain

**Fig. 4(b)**

- Q.5 A) A full wave rectifier using a centre tapped transformer with two diodes gives output of 250V and current is 100 +/- 25mA. If the ripple factor is 0.001, Calculate the specification of the devices and components required if the filter used is LC filter

- B) Explain effect of bypass capacitor and coupling capacitors on frequency response of amplifier [5]

- C) Determine small signal voltage gain of the circuit shown below in Fig 5(c) [5] using hybrid- $\pi$  model. ( $\beta$ =100,V<sub>A</sub>=100V,I<sub>CQ</sub>=0.95m A)

2840 Page 2 of 4

## Q.6 Short notes on: (Attempt any four)

[20]

- a) Small Signal model of diode

- b) Zero temperature drift biasing in JFET amplifier

- c) Explain different types of filters

- d) High frequency hybrid pi equivalent model of CE BJT

- e) Comparison of BJT CE and JFET CS amplifier

12840 Page 3 of 4

12840 Page 4 of 4