(3 hours) Marks: 80

Note the following instructions.

- 1. Question No.1 is compulsory

- 2. Attempt any three questions from remaining five questions

- 3. Solve in total 4 questions

- 4. Assume suitable data wherever necessary, justify the same

- 5. Figures to the right indicate full marks.

- 1.a Mention the different types of faults present in logic circuits and list the method to [5] detect and locate them.

- **1.b** What is a Threshold logic element? Give its advantages and limitations [5]

- 1.c What is a logic hazard and describe in brief the types of logic hazard [5]

- **1.d** Differentiate between Mealy and Moor type state machine. [5]

- **2.a** Use the Quine–McCluskey method to generate the set of essential prime implicants [10] and to obtain the minimal expressions for the following functions.

$$T(w, x, y, z) = \sum (0,1,2,8,9,11,13,15)$$

**2.b** In the following state table, find the equivalence partition and the corresponding reduced machine in standard form. [10]

|                  | NS, z                                |                                      |

|------------------|--------------------------------------|--------------------------------------|

| PS               | x = 0                                | x = 1                                |

| A<br>B<br>C<br>D | F, 0<br>G, 0<br>B, 0<br>C, 0<br>D, 0 | B, 1<br>A, 1<br>C, 1<br>B, 1<br>A, 1 |

| F<br>G           | E, 1<br>E, 1                         | F, 1 $G$ , 1                         |

- **3.a** (i) Give the properties of symmetric function.

- (ii) Decomposed the following function and determine the functions F and  $\Phi$ .

[10]

$$f(v, w, x, y, z) = \sum (1,2,7,9,10,17,19,26,31) + \sum_{\phi} (0,15,20,23,25)$$

=F[\Phi(v,w,y),x,z]

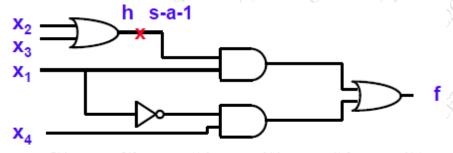

3.b Find all the test vectors that detect input h s-a-1 by using the Path sensitization and the Boolean Differences method.

- **4.a** Show that threshold logic realization of Full Adder requires only two threshold elements. (Note that both sum and carry must be generated)

- **4.b** Explain the synthesis procedure with suitable example for the design of [10] fundamental-mode asynchronous sequential circuits.

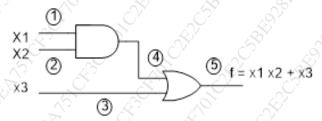

- 5.a Find the fault table for all stuck-at faults of the following circuit [10]

- **5.b** Explain the lattice of closed partitions of machine. [10]

- **6. a** Draw the state diagram and the state table for Moore type sequence detector to detect the sequence 110. [10]

- **6. b** Draw and explian the ASM chart for a weighing machine. [10]

\*\*\*\*\*\*