(Time: 3 Hours) Marks: 80 N.B.: (1)Question No. 1 is compulsory. Solve any three questions from the remaining five (2) Figures to the right indicate full marks (3) Assume suitable data if necessary and mention the same in answer sheet. (4) Attempt any 4 questions. Q.1 [20] Explain bleeder resistor and critical inductance. (a) Explain zero temperature drift biasing. (b) Explain effect of bypass capacitor and coupling capacitors on frequency (c) response of amplifier (d) Draw and explain high frequency model of BJT for CE configuration. Draw and explain small signal model of FET. (e) Q.2 Design single stage RC coupled CS amplifier using self-bias method to meet [15] following specifications: |Av| = 18, Vo = 2.5 Vrms,  $I_{DSS} = 7$  mA,  $g_{mo} = 5600$   $\mu$ S,  $Vp=2.5 \text{ V}, r_d=50 \text{ k}\Omega.$ Calculate Av, Zi and Zo for the circuit designed in Q.2(a). (b) [05] Q.3 A full wave rectifier using a centre tapped transformer with two diodes gives [12] output of 250 V and current is 100 +/- 25 mA. If the ripple factor is 0.001. Calculate the specification of the devices and components required if the filter used is LC filter. (b) Explain the basic fabrication steps of passive elements. [80] What is biasing? What is the need of biasing? Derive the expression for stability Q.4 (a) [10] factor of collector to base bias circuit. Calculate Q-point ( $I_{CO} \& V_{CEO}$ ) and stability factor (S) for the circuit shown in (b) [10] Fig. 4(b).

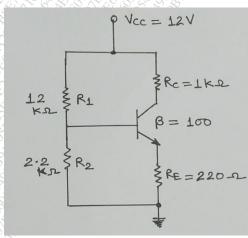

Fig. 4(b)

Q.5 (a) Derive the expressions for Ai, Av, Zi, Zo for CE amplifier with unbypassed  $R_E$ . [15] (b) State and explain Miller's Theorem. [05]

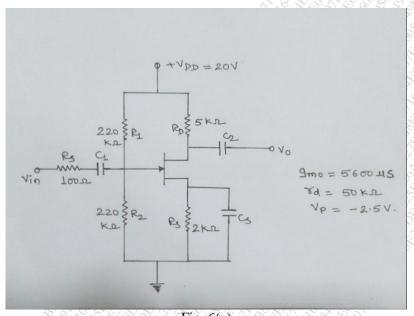

Q.6 (a) Sketch the frequency response for the circuit shown Fig. 6(a) where [15]  $C_1 = 0.5 \mu F$ ,  $C_2 = 1 \mu F$ ,  $C_S = 10 \mu F$ ,  $C_{gs} = 5 \mu F$ ,  $C_{gd} = 2 \mu F$ ,  $C_{ds} = 3 \mu F$ . Take  $I_D = 3 \mu A$ .

Fig. 6(a)

(b) Write a short note on small signal model of diode.

[05]

\*\*\*\*\*\*